PAYLOAD ELECTRONICS

Image Data Handling and Storage Unit for PILOT-D CDIU on-board Luna-Glob Lander (Luna-25)

In the frame of the ESA Lunar exploration program, in cooperation with the Russian Space Agency, primed by Airbus, it is under development a core product, named “PILOT (Precise and Intelligent Landing using On-board Technologies)”, that is a vision-based system providing high precision navigation and autonomous hazard avoidance capabilities during landing.

The PILOT-D demonstrator, consisting of a Camera and a Camera Demonstrator Interface Unit (CDIU) between the camera and the Russian platform, has been developed for the Luna-25 (Luna-Glob) mission (launch currently scheduled for July 2021).

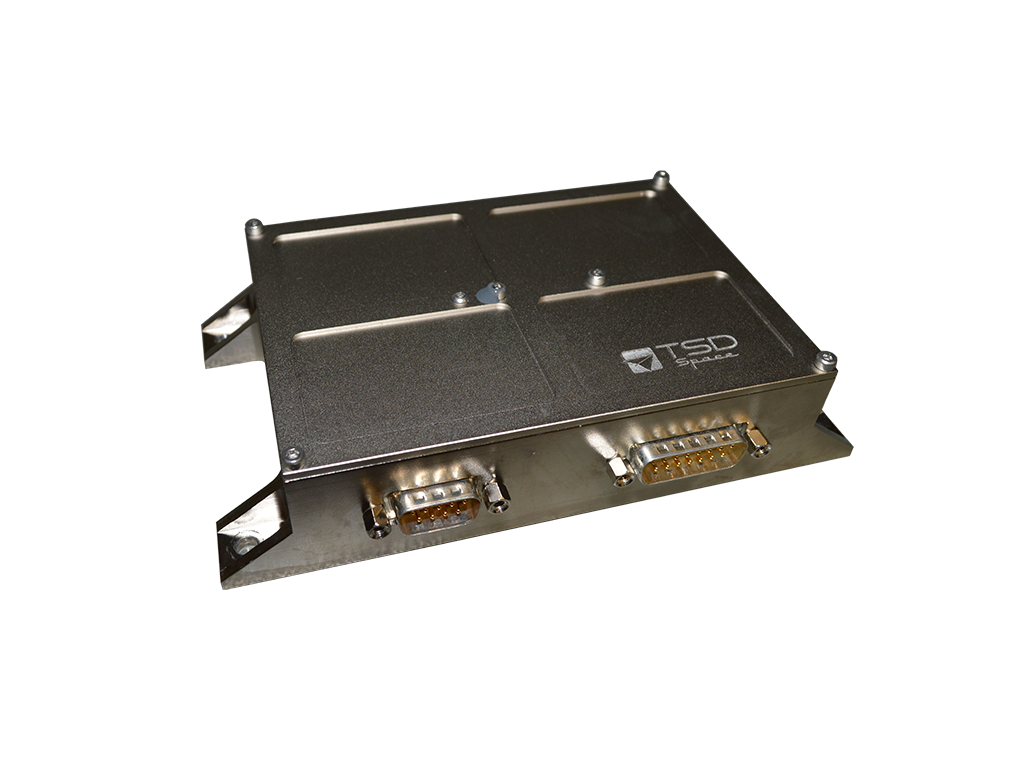

TSD has developed the CDIU that is mainly an “Image Data Handling and Storage Unit” acting as interface unit between the COU and the lander.

The CDIU, in addition to the implementation of communication I/Fs, video data storage and processing, takes also care of the conditioning and distribution of the power to the entire PILOT-D demonstrator.

Multi/Hyperspectral High Data Rate Image Compression Module

The module has been developed by TSD in the framework of the PRISMA Hyperspectral Mission program funded by ASI and it is part of the PRISMA Payload Main Electronics Unit, with the name “SDAC (Scientific Data Acquisition and Compression Module)”.

PRISMA (PRecursore IperSpettrale della Missione Applicativa) Payload is a Hyperspectral Electro-Optical Instrument, designed for an Earth Observation MiniSatellite (<500Kg) that, since the 22nd March 2019, is operatingin a sun synchronous Low Earth Orbit at 615Km, acquiring hyperspectral images in the range from 400 to 2500[nm] and medium resolution panchromatic images.

Multi/Hyperspectral High Data Rate Image Compression Module comprising the upper board as nominal and lower board as redundant.

The module is able of acquiring image data, from the SWIR, VNIR and PAN imagers, reassembling & preprocessing them, performing data compression, applying a CCSDS and Reed Solomon encoding and finally transferring them to the equipment that carry out the storage and transmission to Ground.

The module is provided with a configurable lossless and lossy (near lossless in particular) compression stage, in order to reduce the volume of data to be stored in the mass memory and the transfer rate at an amount compatible with the mass memory input rate and the downlink capability.

Payload Data Processing Unit for Solar Orbiter SWA Instrument

The DPU (Data Processing Unit) is a full redundant rad-hard processing unit that will support the Solar Wind Analyzer suite of four instruments dedicated to the characterization of the solar wind in the frame of the ESA M-class Solar Orbiter mission. The DPU provides power and data communication interfaces with the scientific instruments and the Spacecraft and handles the real-time telecommands, telemetry, data storage and data compression.

TSD has leaded the Italian team in charge of developing the DPU.

- The Solar Orbiter mission is aimed at performing close-up, high-resolution studies of our Sun and inner heliosphere

- At its closest point, the spacecraft will be closer to the Sun than any previous spacecraft (almost one-quarter of Earth’s distance distance from the Sun). It will provide unique data and imagery of the Sun

- The temperature on board the spacecraft will be controlled by means of special radiators, which will dissipate excess heat into space

- The Solar Orbiter accommodates a Payload, with a total payload mass of 180 kg, including a number of instruments, among which the SWA (Solar Wind Analyzer) instrument

- SWA consists of a suite of sensors (EAS1, EAS2, PAS and HIS) and a DPU (Data Processing Unit) that will measure the ion and electron bulk properties (including density, velocity, and temperature) of the solar wind

High Speed Camera Compression Board for ISS EML Facility

Since its launch in August 2014, the Electro-Magnetic Levitator (EML) facility has been one of the most used and successful facility on board the ISS. EML provides the scientific community with the possibility to perform extremely precise measurements on small metallic samples that are heated and melted and then solidified again within an electromagnetic field.

One of the most valuable means for the scientific investigation of the molten samples is the EML High Speed Camera (HSC) that is able to record short videos at more than 30000 frames per second. This has produced a huge amount of video data over the years and in order to optimize the transmission of data to ground, Airbus DS commissioned TSD to design and develop a high-performance compression module to upgrade the existing on-board system (HSC-OS) that performed compression at software level.

The Compression Board HSC-CB will contribute to increase the performance of the entire digital video chain of a factor 5 thus significantly improving the EML community scientific return. The HSC-CB is a PC-104+ module and is part of the HSC-OS unit that is an electronic unit in charge of handling the EML High Speed Camera The HSC-CB receives images from the HSC CPU board over the PCI bus and applies wavelet based hardware compression to achieve different compression levels ranging from lossless up to 100 on images with different dimensions. Both compression factors and image dimensions are fully configurable by the host, the HSC CPU board that is the initiator of the compression session. Compressed images are returned to the host through the PCI bus for subsequent storage onto a mass storage device and transmission to ground during contact periods Ground tests on sample images have proven the quality of the compression output. Images compressed up to a factor 10 are practically undistin-guishable from the original images.

HYDRA Hyperspectral Compression IP core & HW Platform

Under ESA contract, primed by Politecnico of Torino, TSD designed an IP core for FPGA, named HYDRA (Hyperspectral Compression for Very High Data Rate Instruments), of a compression algorithm for multispectral/Hyperspectral images able to operate in three possible modes: lossless/near-lossless/lossy loss-less.

The algorithm was proposed to the MHDC standardization group in order to consider it as the basis of a future CCSDS standard. The same algorithm was subsequently adopted, with the appropriate customizations, also for the compression module developed by TSD for the Hyperspectral Payload of the PRISMA Satellite.

The implemented compression algorithm was based on the predictive lossy compression paradigm and it can be considered as an extension of CCSDS 123 with a quantization stage to achieve lossy compression and a modified entropy coder (range encoder). In addition to the IP core, TSD developed a HW platform based on the industrial grade version of the industry’s first high performance rad-hard reconfigurable Xilinx Virtex XQR5XVFX130. The HW platform is the HPHC (High performance Processing unit for Hyperspecral data Compression), belonging to a family of High performance Processing unit (HPxx) developed by TSD for real time image data processing. HPHC engineering model assembled in its cabinet.

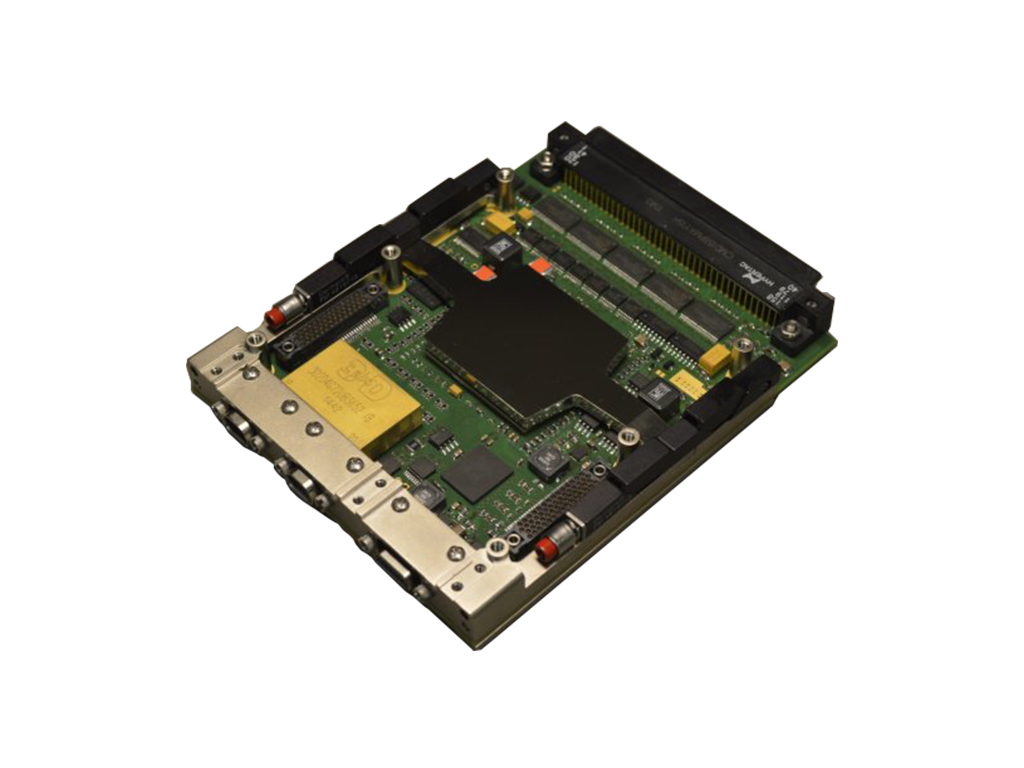

Payload Data Processing Module (PDPM) for Very Small Space Platform

The Payload Data Processing Module (PDPM), based on the powerful Virtex5QV FPGA, is characterized by a high grade of compactness and can be adopted on board very small platform, for Instruments requiring large computational and/or storage resources and for low cost missions, like LEO Small Satellite and in general for Missions with low radiation tolerance requirements.

The realization of the module, completed by TSD on 2015, has been carried out in the frame of an ESA funded program for technological developments. Purpose of the program was the realization of a LEON-based CPU module with reduced SWaP (Size, Weight and Power) but with advanced data handling and storage capabilities.

That module presents the following architecture and main specifications:

- LEON3 IP core as module controller

- SATA controller for data storage on SATA solid state devices

- HW acceleration for compression and data processing algorithms

- Input data preprocessing and output data encoding

- Input data rate up to 6.3Gbits/s

- 2 output SpaceWire links up to 100Mbits/s and 1 output MultiGbit link (compatible with SpaceFibre) up to 2.5Gbits/s

The Virtex-5 FPGA is employed as a complex SoC (System-on-Chip), hosting the LEON3 CPU, all the foreseen peripherals and implementing the processing algorithms.

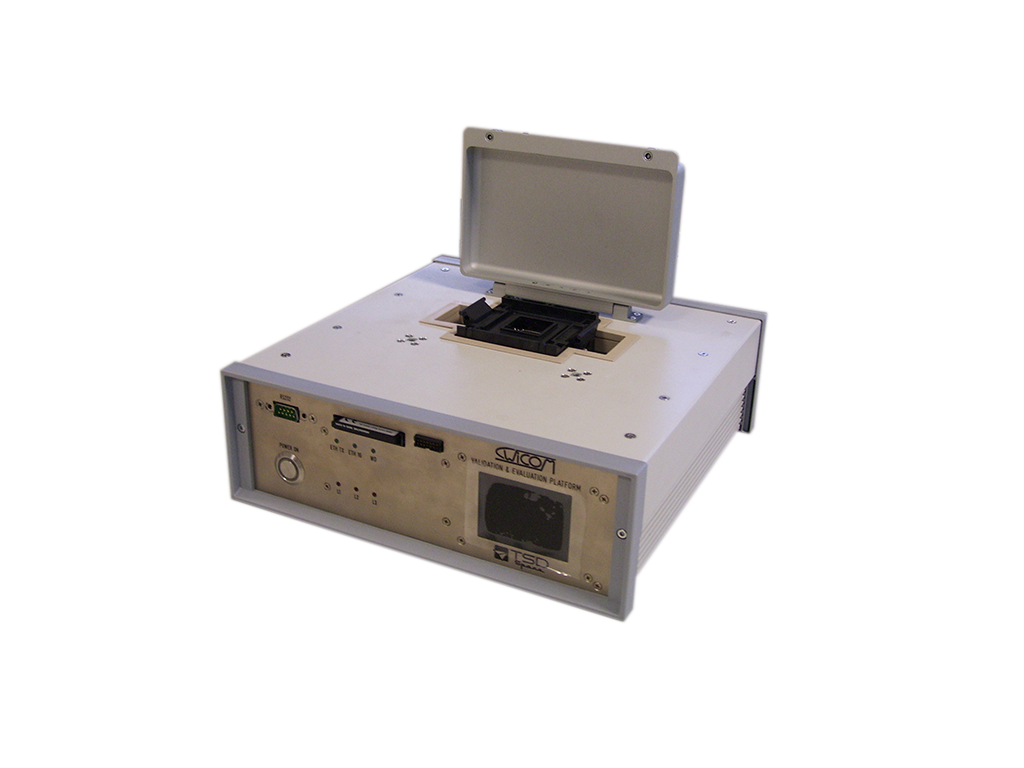

CWICOM Validation & Evaluation Platform

The TSD CWICOM (CCSDS Wavelet Image Compression ASIC) Validation & Evaluation Platform provides all the data handling and interfaces resources to prototype the CWICOM RTL code with FPGA and to test the ASIC samples, both in a representative H/W environment.

The available interfaces are:

CWICOM Validation & Evaluation Platform

- 220 V AC power input

- CameraLink or Parallel LVDS video input

- Ctrl/Cfg Gigabit Ethernet Port

- RS232 Debug UART line

- Compact-flash Card connector

- SpaceWire Interface

- Standard socket to host CWICOM sample

- Virtex-5 FPGA to prototype RTL code The platform can be customized for different ASICs

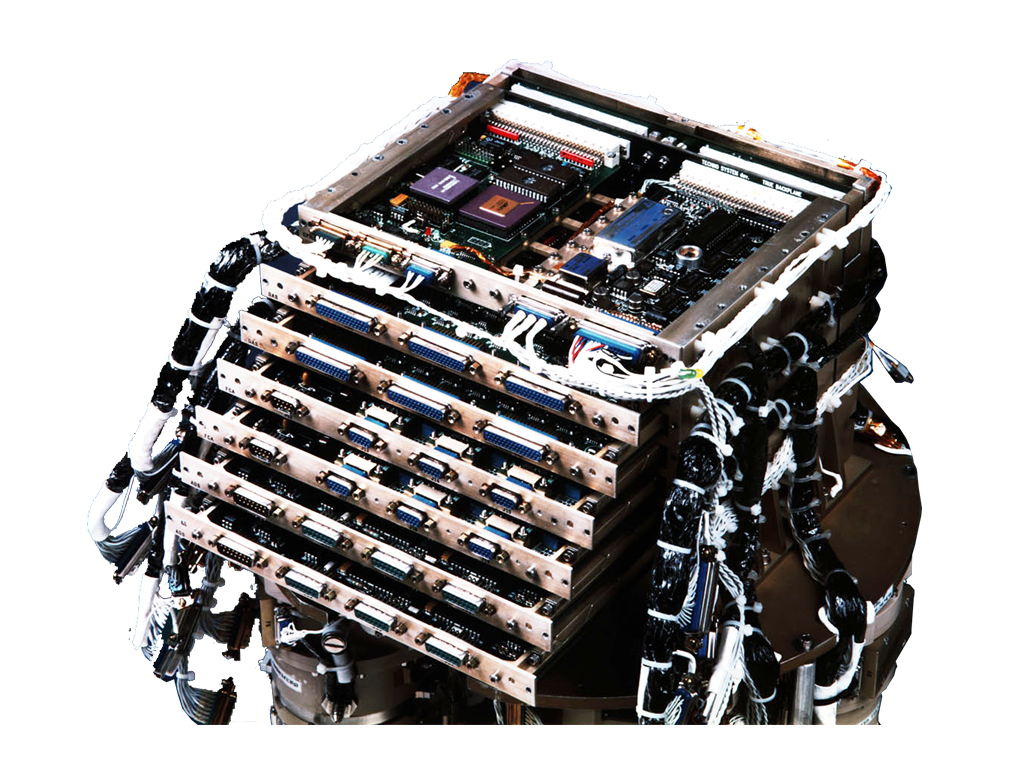

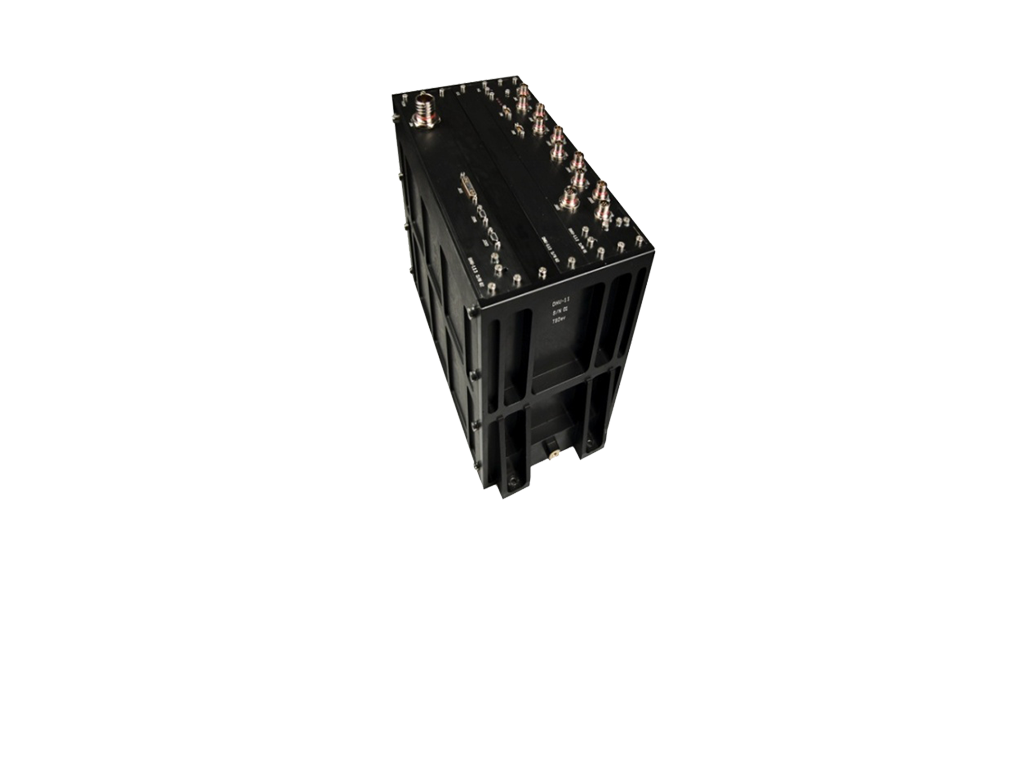

Data handling Unit for Foton Satellite Payload

FOTON is a Russian unmanned capsule launched into near-circular low-earth orbits providing excellent microgravity levels (≈10-5 g) for 2-week missions

TSD has participated to the last 4 FOTON missions (FOTON12, M1, M2, M3) in the frame of TeleSupport project, that foresaw the realization of an advanced data handling equipment (DHU) that provided the scientific payloads on-board with real-time management of telecommands, telemetry and digital video. During the last mission (M3) the DHU has been interfaced to ten experimental payloads.

Control & Data Acquisition Systems for Scientific Payload & Instruments

TSD develops dedicated Control and Data Acquisition Systems (CDAS) capable of providing Scientific Payloads with a complete, integrated and low resources demanding platform including:

- Experiment Computers

- Real time data processing subunits

- Data Acquisition subunits for a wide range of sensors (temperature, pressure, estensimeters, accelerometers, strain gauges, force sensors….)

- Actuator Drivers subunits for a wide range of actuators (stepper motors, DC motors, brushless motors, injection device, heaters, peltiers, …)

- Battery subunits

- Power conditioning and distribution subunits

- Dedicated experiment and data management interfaces